# Simulink® HDL Coder 1 User's Guide

#### How to Contact The MathWorks

www.mathworks.com

comp.soft-sys.matlab

www.mathworks.com/contact TS.html Technical Support

Web

Newsgroup

suggest@mathworks.com bugs@mathworks.com

doc@mathworks.com

service@mathworks.com info@mathworks.com

Product enhancement suggestions

Bug reports

Documentation error reports

Order status, license renewals, passcodes Sales, pricing, and general information

508-647-7000 (Phone)

508-647-7001 (Fax)

The MathWorks, Inc. 3 Apple Hill Drive Natick, MA 01760-2098

For contact information about worldwide offices, see the MathWorks Web site.

Simulink HDL Coder User's Guide

© COPYRIGHT 2006–2007 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB, Simulink, Stateflow, Handle Graphics, Real-Time Workshop, SimBiology, SimHydraulics, SimEvents, and xPC TargetBox are registered trademarks and The MathWorks, the L-shaped membrane logo, Embedded MATLAB, and PolySpace are trademarks of The MathWorks, Inc.

ModelSim is a registered trademark of Mentor Graphics Corporation.

Incisive® is a registered trademark of Cadence Design Systems.

Other product or brand names are trademarks or registered trademarks of their respective holders.

#### **Patents**

The MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

### **Revision History**

September 2006 Online only

March 2007 Online only

September 2007 Online only

New for Version 1.0 (Release 2006b) Updated for Version 1.1 (Release 2007a) Revised for Version 1.2 (Release 2007b)

## **Getting Started**

| What Is Simulink HDL Coder?                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overview                                                                                                                                                                           |

| Simulink HDL Coder in the Hardware Development                                                                                                                                     |

| Process                                                                                                                                                                            |

| Summary of Key Features                                                                                                                                                            |

| Expected Users and Prerequisites                                                                                                                                                   |

| Software Requirements and Installation                                                                                                                                             |

| Software Requirements                                                                                                                                                              |

| Installing the Software                                                                                                                                                            |

| Available Help and Demos                                                                                                                                                           |

| Online Help                                                                                                                                                                        |

| Demos                                                                                                                                                                              |

| Introduction to HDL Code Genera                                                                                                                                                    |

| Overview of Exercises                                                                                                                                                              |

|                                                                                                                                                                                    |

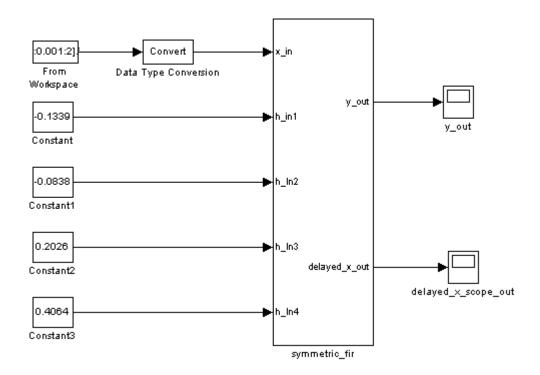

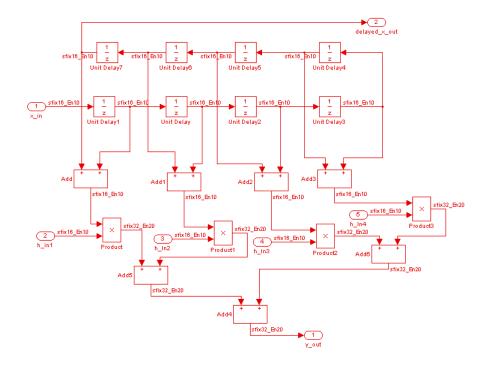

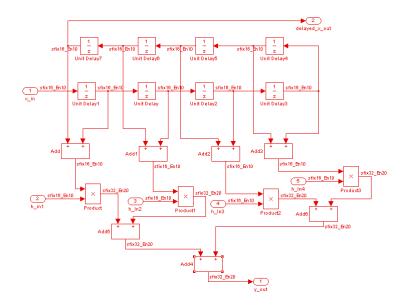

| The sfir_fixed Demo Model                                                                                                                                                          |

|                                                                                                                                                                                    |

| The sfir_fixed Demo Model                                                                                                                                                          |

| The sfir_fixed Demo Model  Generating HDL Code Using MATLAB Commands  Overview                                                                                                     |

| The sfir_fixed Demo Model  Generating HDL Code Using MATLAB Commands  Overview  Creating a Directory and Local Model File  Initializing Model Parameters with hdlsetup             |

| Generating HDL Code Using MATLAB Commands Overview Creating a Directory and Local Model File Initializing Model Parameters with hdlsetup Generating a VHDL Entity from a Subsystem |

| The sfir_fixed Demo Model                                                                                                                                                          |

|     | Generating a Verilog Module and Test Bench                                                                                                                                                                                                                                                       |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

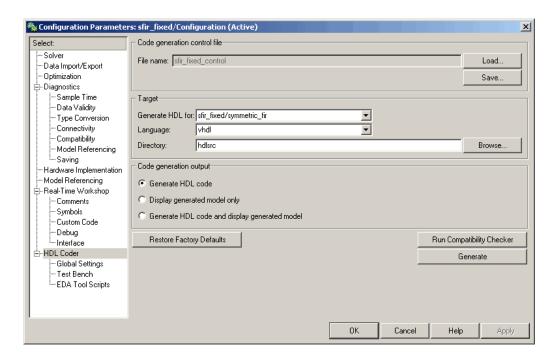

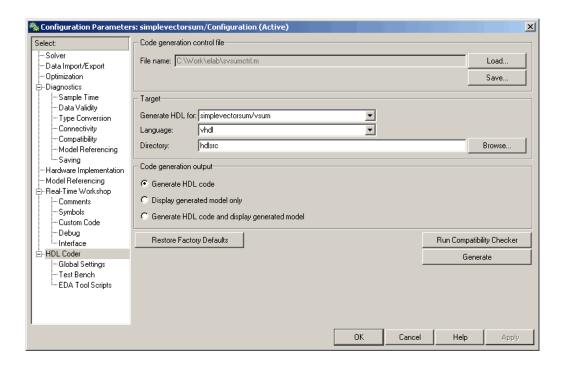

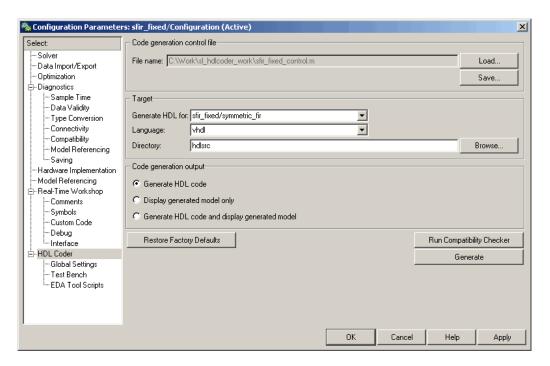

| G   | enerating HDL Code in the Simulink GUI                                                                                                                                                                                                                                                           |    |

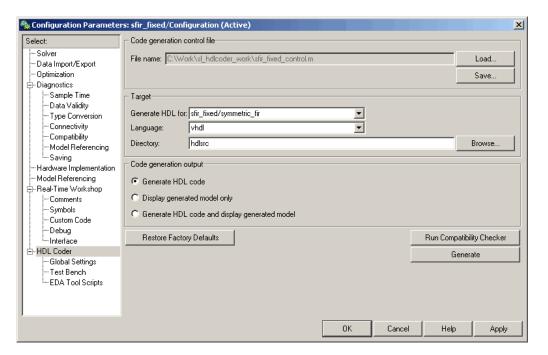

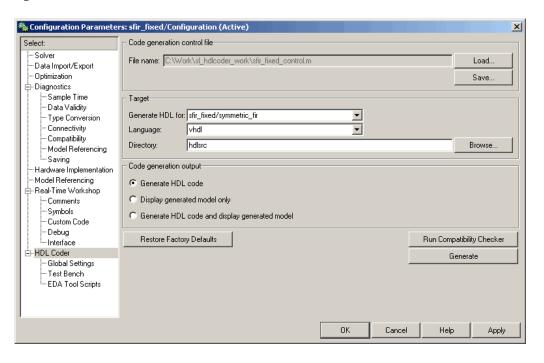

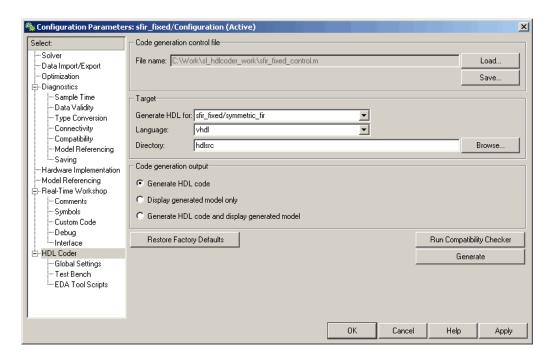

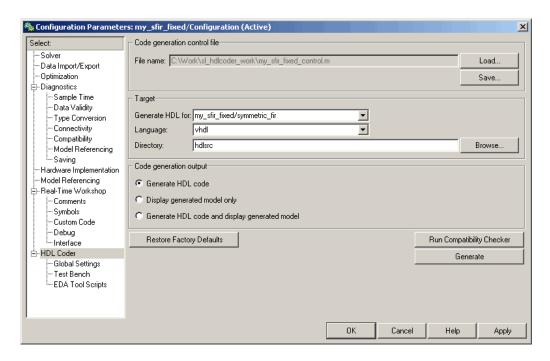

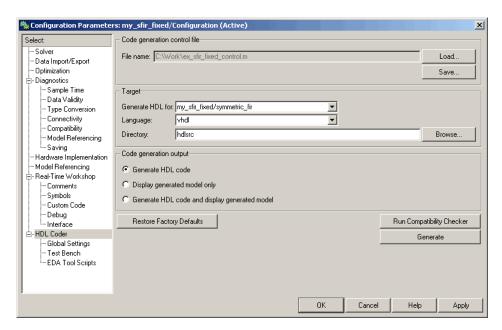

|     | Creating a Directory and Local Model File Viewing Simulink HDL Coder Options in the Configuration                                                                                                                                                                                                |    |

|     | Parameters Dialog Box                                                                                                                                                                                                                                                                            |    |

|     | Creating a Control File                                                                                                                                                                                                                                                                          |    |

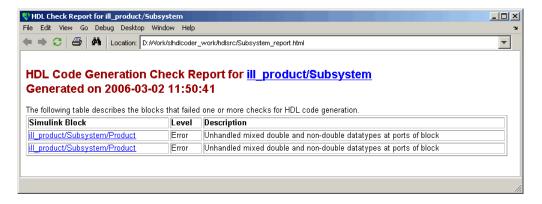

|     | Initializing Model Parameters With hdlsetup Selecting and Checking a Subsystem for HDL                                                                                                                                                                                                           |    |

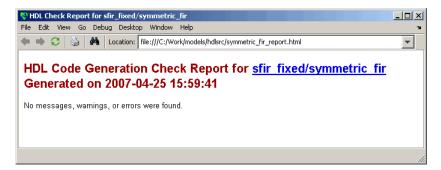

|     | Compatibility                                                                                                                                                                                                                                                                                    |    |

|     | Generating VHDL Code                                                                                                                                                                                                                                                                             |    |

|     | Generating VHDL Test Bench Code                                                                                                                                                                                                                                                                  |    |

|     | Verifying Generated Code                                                                                                                                                                                                                                                                         |    |

|     | denotating verify frout and rest Bonon code ************************************                                                                                                                                                                                                                 |    |

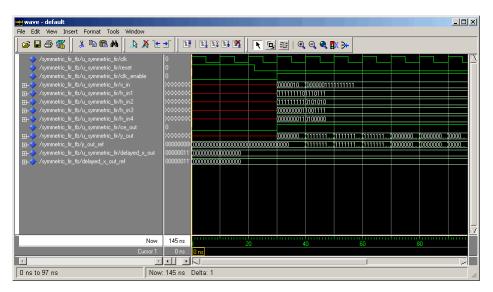

| Si  | imulating and Verifying Generated HDL Code                                                                                                                                                                                                                                                       |    |

| (   | Code Generation Options in the Simulink I<br>Coder                                                                                                                                                                                                                                               | H  |

|     | Coder                                                                                                                                                                                                                                                                                            | H  |

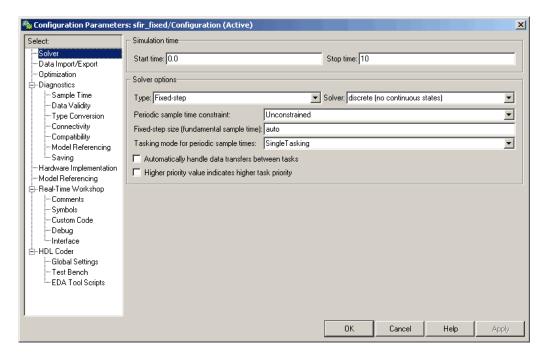

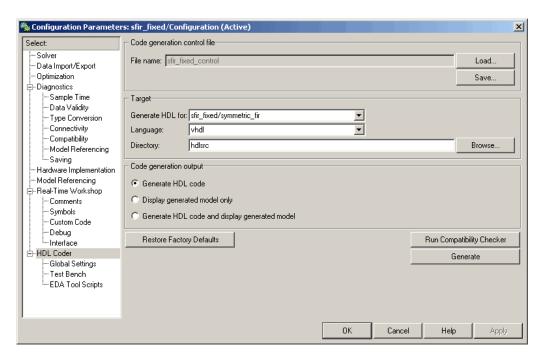

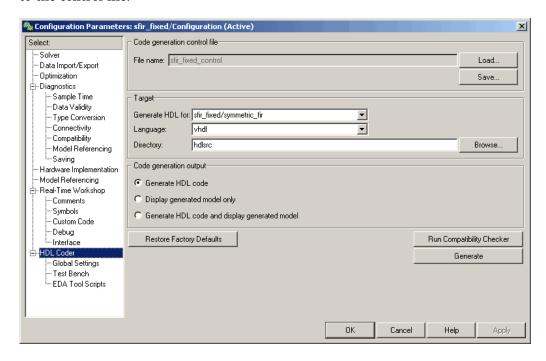

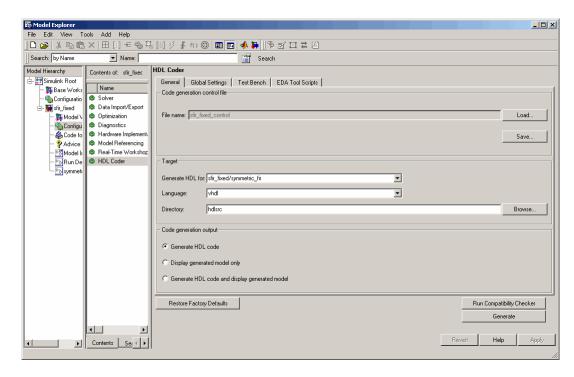

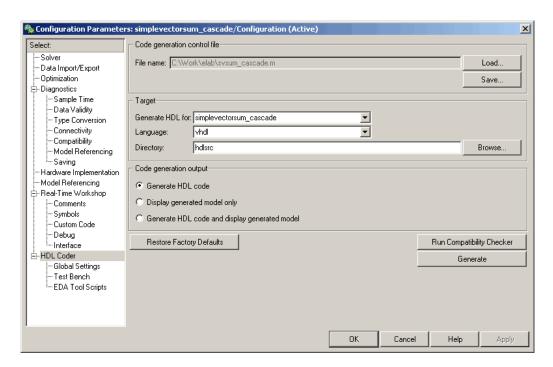

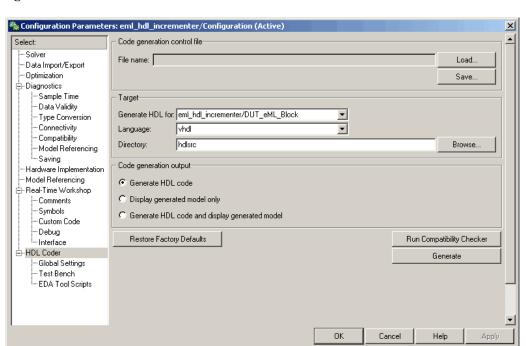

|     | Code Generation Options in the Simulink I Coder  iewing and Setting HDL Coder Options  HDL Coder Options in the Configuration Parameters Dialog                                                                                                                                                  | H  |

|     | iewing and Setting HDL Coder Options  HDL Coder Options in the Configuration Parameters Dialog Box                                                                                                                                                                                               | H  |

|     | iewing and Setting HDL Coder Options  HDL Coder Options in the Configuration Parameters Dialog Box                                                                                                                                                                                               | H  |

|     | iewing and Setting HDL Coder Options  HDL Coder Options in the Configuration Parameters Dialog Box                                                                                                                                                                                               | H  |

| V   | iewing and Setting HDL Coder Options  HDL Coder Options in the Configuration Parameters Dialog Box                                                                                                                                                                                               | H  |

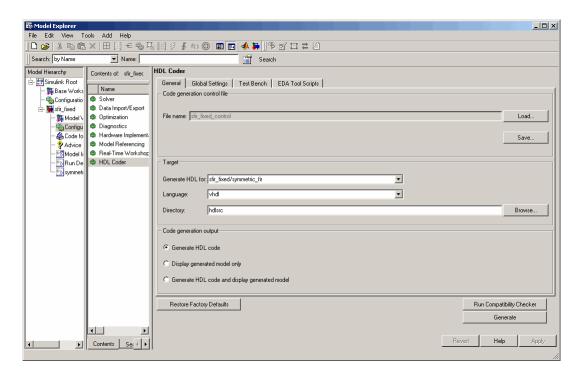

| V   | iewing and Setting HDL Coder Options  HDL Coder Options in the Configuration Parameters Dialog Box  HDL Coder Options in the Model Explorer  HDL Coder Menu                                                                                                                                      | HG |

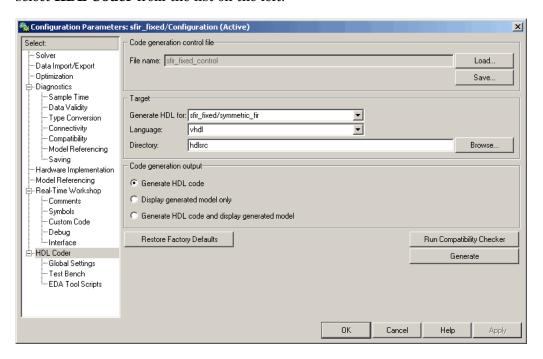

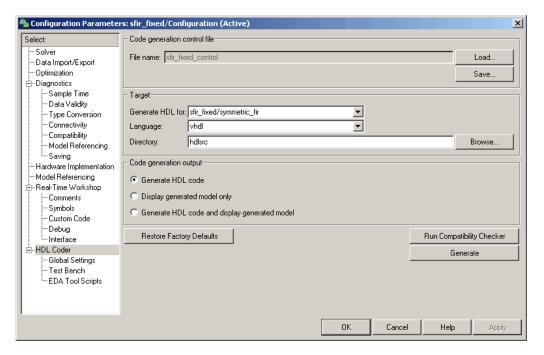

| V   | iewing and Setting HDL Coder Options  HDL Coder Options in the Configuration Parameters Dialog Box  HDL Coder Options in the Model Explorer  HDL Coder Menu  DL Coder Pane: General  HDL Coder Top-Level Pane Overview  File name                                                                | H  |

| V   | iewing and Setting HDL Coder Options  HDL Coder Options in the Configuration Parameters Dialog Box  HDL Coder Options in the Model Explorer  HDL Coder Menu  DL Coder Pane: General  HDL Coder Top-Level Pane Overview  File name  Generate HDL for                                              | G  |

| V   | iewing and Setting HDL Coder Options  HDL Coder Options in the Configuration Parameters Dialog Box  HDL Coder Options in the Model Explorer  HDL Coder Menu  DL Coder Pane: General  HDL Coder Top-Level Pane Overview  File name  Generate HDL for  Language                                    | G  |

| V   | iewing and Setting HDL Coder Options  HDL Coder Options in the Configuration Parameters Dialog Box  HDL Coder Options in the Model Explorer  HDL Coder Menu  DL Coder Pane: General  HDL Coder Top-Level Pane Overview  File name  Generate HDL for  Language  Directory                         | G  |

| V   | iewing and Setting HDL Coder Options  HDL Coder Options in the Configuration Parameters Dialog Box  HDL Coder Options in the Model Explorer  HDL Coder Menu  DL Coder Pane: General  HDL Coder Top-Level Pane Overview  File name  Generate HDL for  Language                                    | G  |

| V   | iewing and Setting HDL Coder Options  HDL Coder Options in the Configuration Parameters Dialog Box  HDL Coder Options in the Model Explorer  HDL Coder Menu  DL Coder Pane: General  HDL Coder Top-Level Pane Overview  File name  Generate HDL for  Language  Directory  Code Generation Output | G  |

| V H | iewing and Setting HDL Coder Options  HDL Coder Options in the Configuration Parameters Dialog Box  HDL Coder Options in the Model Explorer  HDL Coder Menu  DL Coder Pane: General  HDL Coder Top-Level Pane Overview  File name  Generate HDL for  Language  Directory                         | G  |

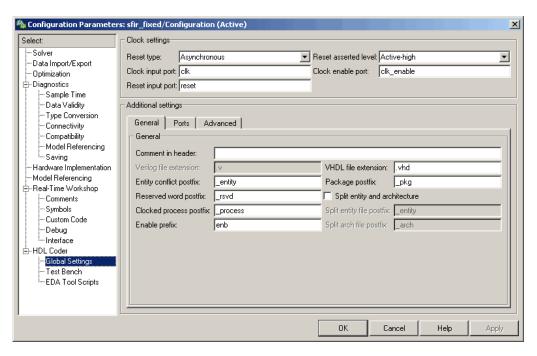

| Reset asserted level                    | 3-17         |

|-----------------------------------------|--------------|

| Clock input port                        | 3-18         |

| Clock enable port                       | 3-19         |

| Reset input port                        | 3-20         |

| Comment in header                       | 3-21         |

| Verilog file extension                  | 3-22         |

| VHDL file extension                     | 3-23         |

| Entity conflict postfix                 | 3-24         |

| Package postfix                         | 3-25         |

| Reserved word postfix                   | 3-26         |

| Split entity and architecture           | 3-27         |

|                                         | 3-29         |

| Split entity file postfix               | 3-30         |

| Clearly description                     | 3-30<br>3-31 |

| Clocked process postfix                 |              |

| Enable prefix                           | 3-32         |

| Input data type                         | 3-33         |

| Output data type                        | 3-34         |

| Clock enable output port                | 3-36         |

| Represent constant values by aggregates | 3-37         |

| Use "rising_edge" for registers         | 3-39         |

| Loop unrolling                          | 3-40         |

| Cast before sum                         | 3-41         |

| Use Verilog `timescale directives       | 3-42         |

| Inline VHDL configuration               | 3-43         |

| Concatenate type safe zeros             | 3-44         |

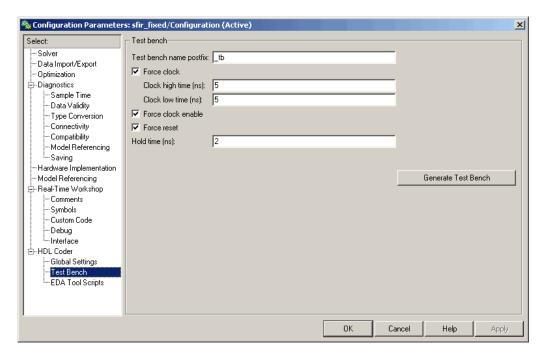

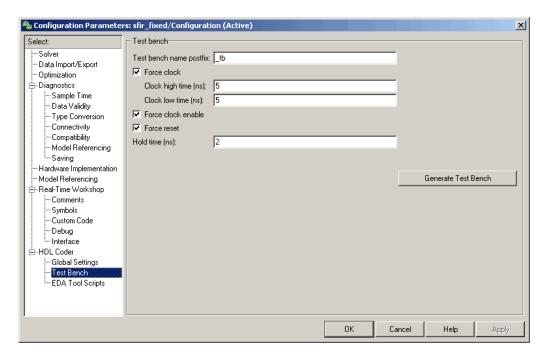

| HDL Coder Pane: Test Bench              | 3-45         |

| Test Bench Overview                     | 3-46         |

| Test bench name postfix                 | 3-47         |

| Force clock enable                      | 3-48         |

| Force clock                             | 3-49         |

| Clock high time (ns)                    | 3-50         |

| Clock low time (ns)                     | 3-51         |

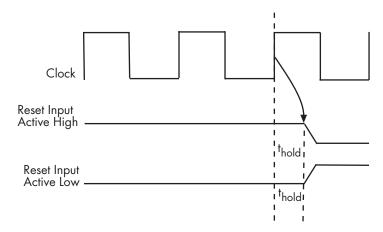

| Force reset                             | 3-52         |

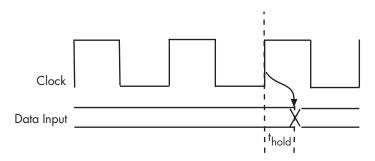

| Hold time (ns)                          | 3-53         |

| Tiona vinic (iii)                       | 0 00         |

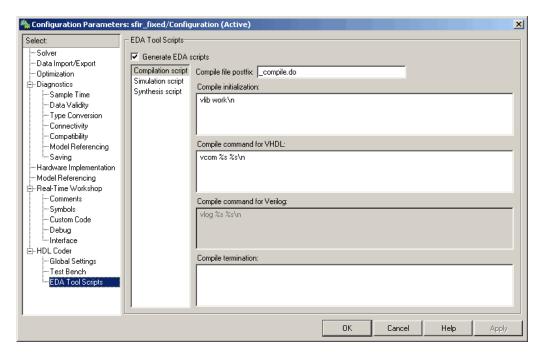

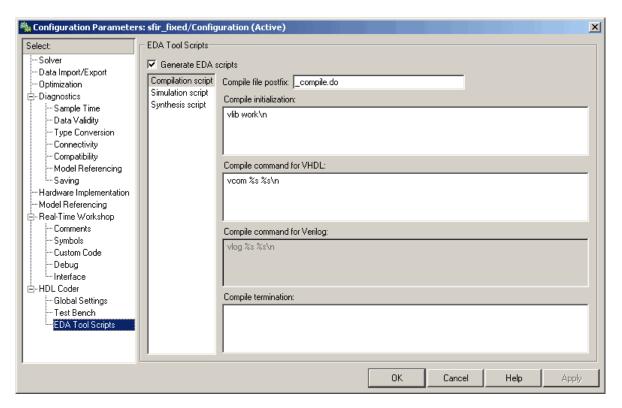

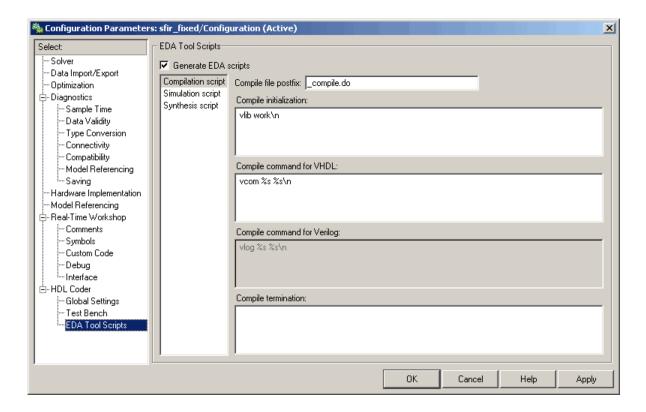

| HDL Coder Pane: EDA Tool Scripts        | 3-54         |

| EDA Tool Scripts Overview               | 3-56         |

| Generate EDA scripts                    | 3-57         |

| Compile file postfix                    | 3-58         |

| Compile Initialization                  | 3-59         |

| Compile command for VHDL                | 3-60         |

| Compile command for Verilog             | 3-61         |

| Code Generation Control                                    |     |

|------------------------------------------------------------|-----|

| Code Generation Control                                    | Fi] |

|                                                            |     |

| ClockEnableDelay                                           |     |

| HoldInputDataBetweenSamples                                |     |

| Overview                                                   |     |

| Properties Supporting Multirate Code Generation            |     |

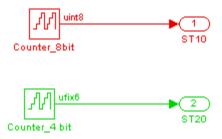

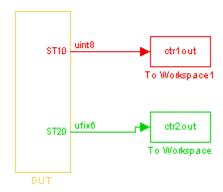

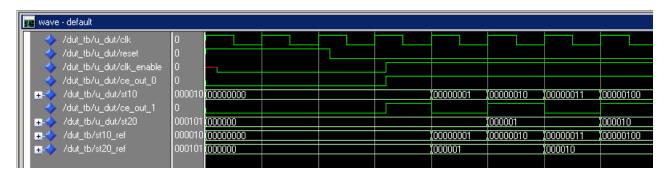

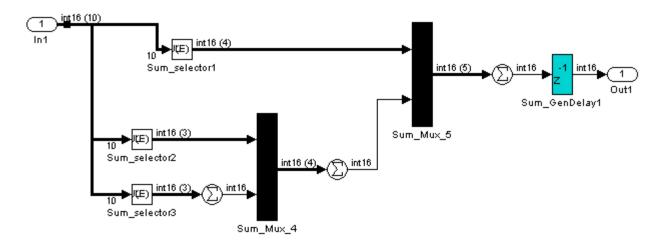

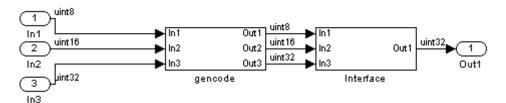

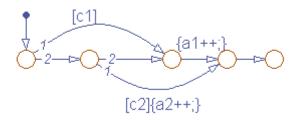

| Example: Model With a Multirate DUT                        |     |

| Multirate Models                                           |     |

| Constraints for Rate Transition Blocks and Other Blocks in |     |

| Configuring Sample Rates in the Model                      |     |

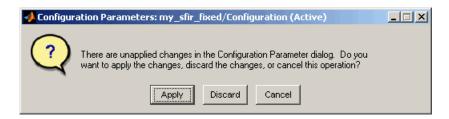

| Configuring Model Parameters                               |     |

| Overview                                                   |     |

| Configuring Multirate Models for HDL Code Generation       |     |

| Overview                                                   |     |

|                                                            |     |

| Generating HDL Code for Multirate Mo                       | ode |

|                                                            |     |

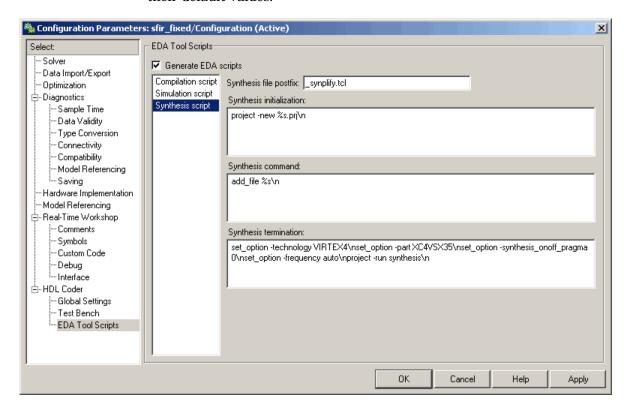

| Synthesis termination                                      | 3   |

| Synthesis initialization                                   | 9   |

| Synthesis file postfix                                     | 9   |

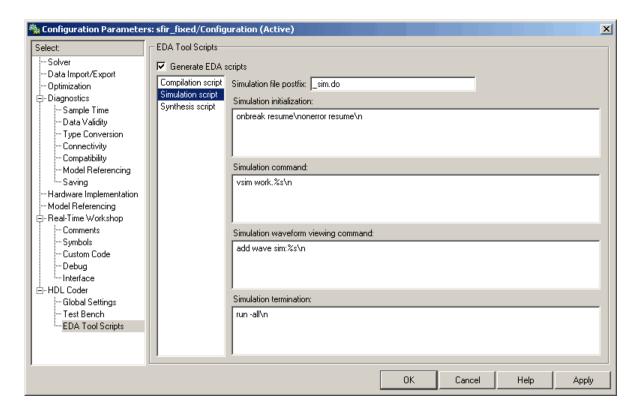

| Simulation termination                                     | 3   |

| Simulation waveform viewing command                        | 3   |

|                                                            | 3   |

| Simulation initialization                                  | 3   |

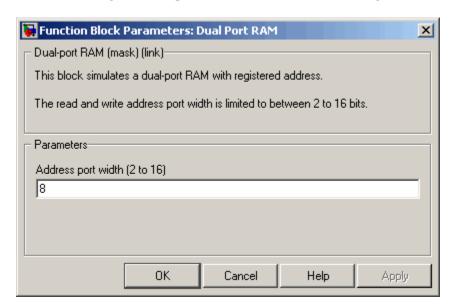

| Selectable Block Implementations and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5  |

| Implementation Mappings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5  |

| Control File Demo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5  |

| Structure of a Control File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5  |

| Code Generation Control Objects and Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5  |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5  |

| hdlnewcontrol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5  |

| forEach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5  |

| forAll                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5- |

| set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5- |

| generateHDLFor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5- |

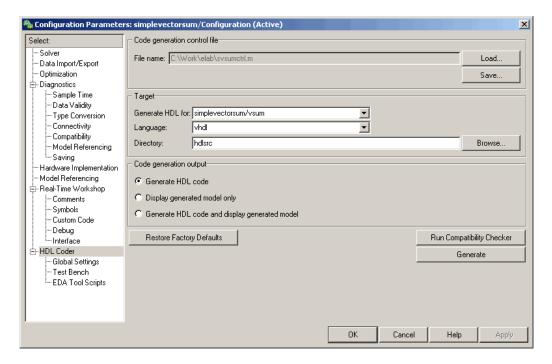

| Using Control Files in the Code Generation Process Creating a Control File and Saving Your HDL Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5- |

| Generation Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5- |

| Associating an Existing Control File with Your Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5- |

| Detaching a Control File from Your Model Setting Up HDL Code Generation Defaults With a Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5  |

| File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5- |

| Specifying Block Implementations and Parameters in the Control File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5- |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5- |

| hdlnewforeach Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5- |

| Blocks with Multiple Implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5- |

| Summary of Block Implementations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5- |

| Block Implementation Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5- |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5- |

| OutputPipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5- |

| Interface Generation Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5- |

| Restrictions on Use of Blocks in the Test Rench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5. |

| NASCRIPTION OF THE PROPERTY OF THE PARTY OF |    |

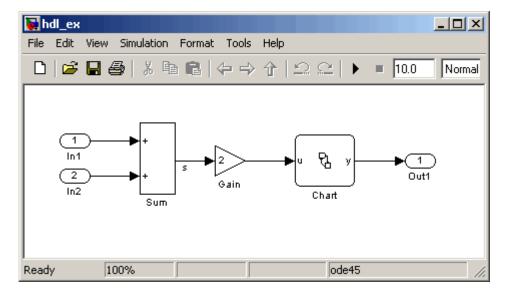

| <b>Generating Bit-True</b> | Cycle-Accurate | Models |

|----------------------------|----------------|--------|

|----------------------------|----------------|--------|

| 6        |                                                       |             |

|----------|-------------------------------------------------------|-------------|

|          | Overview of Generated Models                          | 6-2         |

|          | Example: Numeric Differences                          | 6-4         |

|          | Example: Latency                                      | 6-8         |

|          | Defaults and Options for Generated Models             | 6-12        |

|          | Defaults for Model Generation                         | 6-12        |

|          | GUI Options                                           | 6-13        |

|          | Generated Model Properties for makehdl                | 6-14        |

|          | Fixed-Point and Double Precision Limitations for      |             |

|          | Generated Models                                      | 6-17        |

|          | Fixed-Point Limitation                                | 6-17        |

|          | Double Precision Limitation                           | 6-17        |